數字集成電路設計的里程表 從概念到實現的精密之旅

里程表,作為測量和顯示車輛行駛距離的核心儀表,其核心已從傳統的機械式、機電式全面進化到以數字集成電路(IC)為主導的現代電子系統。基于數字集成電路的設計,不僅賦予了里程表前所未有的精度、可靠性和功能多樣性,也深刻體現了微電子技術在汽車工業中的滲透與革新。這一設計旅程,宛如一個精密的“里程表”,記錄著從抽象需求到硅晶圓上實體電路的每一個技術里程碑。

第一站:需求分析與系統架構定義

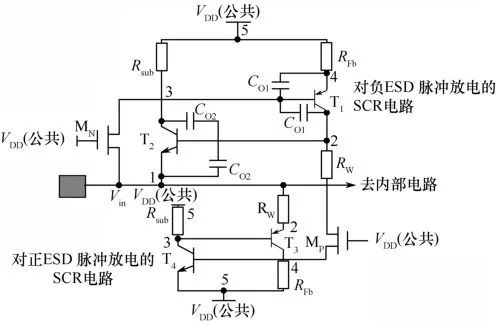

設計之旅始于明確的需求:高精度計量車輪轉數、抗汽車電子環境干擾(如電壓波動、溫度變化、電磁兼容)、低功耗、以及可能需要的多功能集成(如瞬時/平均速度計算、行程記憶、故障診斷等)。在此基礎上,系統架構師將整個里程表系統劃分為傳感器接口、核心處理單元、數據存儲和顯示驅動等關鍵模塊。此時,決策的核心是選擇采用全定制ASIC(專用集成電路)、半定制(如基于FPGA原型)還是利用成熟微控制器(MCU)配合外圍專用電路來實現。對于追求極致集成度、成本與功耗的批量應用,全定制或半定制數字IC成為首選。

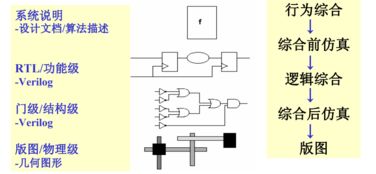

第二站:數字邏輯設計與硬件描述語言(HDL)編碼

這是設計的核心階段。工程師使用Verilog或VHDL等硬件描述語言,將系統架構轉化為嚴格的數字邏輯行為描述。關鍵設計包括:

- 信號調理與脈沖整形模塊:處理來自車速傳感器(如霍爾傳感器或光電傳感器)的脈沖信號,濾除抖動噪聲,生成干凈的時鐘脈沖。

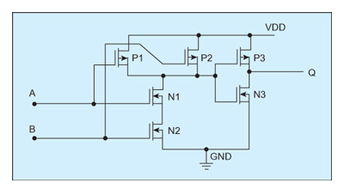

- 核心計數與運算模塊:這是里程表的“大腦”。一個精密的計數器對車輪脈沖進行累計。更重要的是,需要根據輪胎周長等參數,通過乘法器、累加器等數字運算單元,將脈沖數轉換為實際里程(通常以公里或英里為單位)。此部分設計需特別注意溢出處理和計算精度。

- 控制與接口模塊:負責協調各模塊工作,管理里程數據的存儲(通常使用非易失性存儲器如EEPROM的控制器接口),以及提供與車輛總線(如CAN)或顯示單元的通信接口(如SPI、I2C或直接驅動段碼LCD/OLED的控制器)。

第三站:仿真驗證與綜合

在代碼編寫完成后,利用仿真工具(如ModelSim)構建測試平臺,注入各種測試向量(包括正常脈沖、極端頻率、干擾信號等), rigorously驗證邏輯功能的正確性、時序的滿足性以及邊界情況下的行為。確認無誤后,使用邏輯綜合工具(如Design Compiler),將HDL代碼映射到目標工藝庫(如某代CMOS工藝)的標準邏輯門單元上,生成門級網表。這一過程需要設定面積、時序(建立/保持時間)和功耗的約束,以優化最終電路。

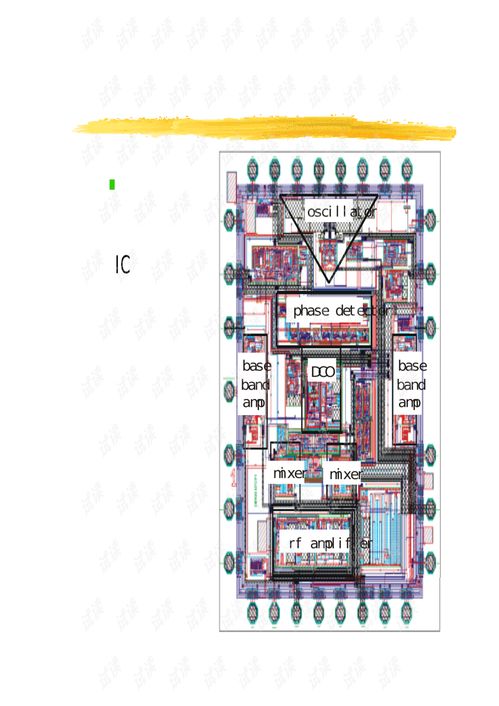

第四站:后端物理設計與簽核

門級網表仍需轉換為具體的物理布局。后端設計流程包括:

- 布局規劃:在芯片版圖上規劃模塊、電源網絡的位置。

- 放置與布線:將各個邏輯單元放置在芯片上,并用金屬線進行連接。對于里程表IC,需特別關注模擬模塊(如電源管理、傳感器輸入緩沖)與數字模塊的隔離,以及時鐘信號的分布,確保信號完整性。

- 時序分析與收斂:提取布線后的寄生參數,進行更精確的時序分析,確保在所有工藝角(Process Corner)、電壓和溫度(PVT)變化下,電路仍能正確工作。

- 物理驗證:進行設計規則檢查(DRC)和版圖與電路圖一致性檢查(LVS),確保版圖符合晶圓廠的制造規則且與原始電路一致。

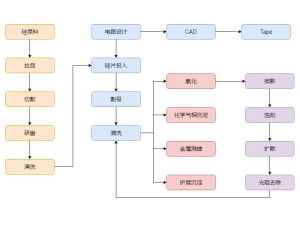

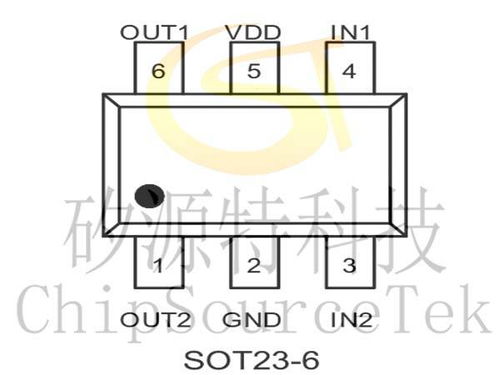

第五站:流片、測試與系統集成

通過所有驗證后,設計數據交付晶圓廠進行流片制造。芯片返回后,進行嚴格的測試,包括功能測試、性能測試和可靠性測試(如高溫工作壽命測試)。測試合格的數字IC里程表芯片,隨后被封裝,并焊接在車輛的儀表盤PCB上,與傳感器、顯示器和車輛電源系統集成,最終成為駕駛員眼前那個穩定跳動的數字。

技術演進與未來趨勢

現代數字IC里程表的設計日益復雜和智能:

- 高集成度:將微控制器內核、存儲器、模擬前端、電源管理及多種接口集成于單顆SoC(片上系統)中。

- 功能安全:遵循ISO 26262標準,設計內建自測試(BIST)、冗余校驗等機制,以滿足汽車ASIL等級要求。

- 車聯網集成:里程數據可通過車載網絡上傳,用于車隊管理、保險定制(UBI)及智能交通系統。

****

設計一款用于里程表的數字集成電路,是一次跨越算法、邏輯、電路與物理實現的完整工程實踐。它如同其測量對象——里程一樣,每一步都需精確無誤。從脈沖到里程的轉換,不僅在輪胎的旋轉中完成,更在硅晶片的納米級結構中,通過數百萬個晶體管井然有序的開關動作而實現。這枚小小的芯片,不僅是車輛行駛距離的忠實記錄者,其本身的設計歷程,也鐫刻著現代集成電路產業向著更高集成、更低功耗、更可靠應用不斷邁進的堅實足跡。

如若轉載,請注明出處:http://www.aaaaadesign.cn/product/73.html

更新時間:2026-03-01 06:49:02