CMOS模擬集成電路版圖設計第五章 Calibre驗證文件詳解與集成電路設計流程

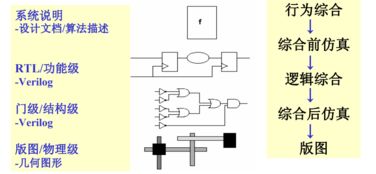

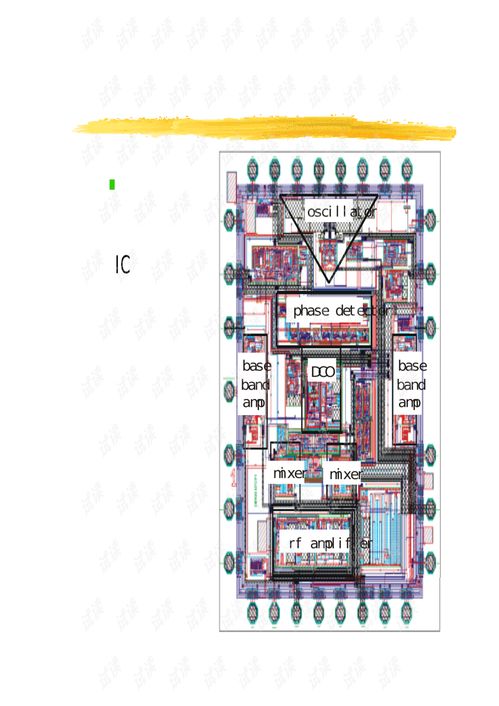

集成電路設計是一個高度復雜且嚴謹的過程,其中版圖設計完成后,必須通過一系列嚴格的物理驗證才能確保芯片功能的正確性與制造的可靠性。Calibre作為業界領先的物理驗證工具,其驗證文件的編寫與執行是連接設計與制造的關鍵橋梁。本章將深入探討Calibre驗證文件的基礎、核心方法及其在集成電路設計流程中的關鍵作用。

一、Calibre驗證文件基礎:DRC、LVS與ERC

Calibre驗證主要包含三大核心部分:設計規則檢查(DRC)、版圖與電路圖一致性檢查(LVS)和電氣規則檢查(ERC)。

- 設計規則檢查(DRC):這是物理驗證的首要步驟。DRC文件(通常以

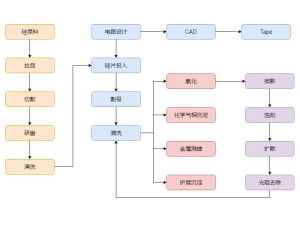

.calibre或.drv為擴展名)由代工廠(Foundry)提供,其中定義了芯片制造工藝所必須遵守的所有幾何規則。例如,晶體管的最小溝道長度、金屬線的最小寬度和間距、接觸孔的大小及覆蓋范圍等。Calibre DRC工具會根據這些規則,自動檢查版圖中所有圖形層是否存在違反規則的情況,并生成詳細的錯誤報告。確保DRC Clean是版圖流片(Tape-out)的基本前提。

- 版圖與電路圖一致性檢查(LVS):LVS驗證旨在確保實際繪制的版圖(Layout)與電路設計原理圖(Schematic)在電氣連接上完全一致。LVS驗證文件(通常包含

.calibre、.lvs等文件)會提取版圖中的器件(如MOS管、電阻、電容)和連接關系(Netlist),并與原理圖網表進行比對。LVS驗證不僅檢查器件類型、數量是否匹配,更重要的是驗證所有節點的連接關系是否正確。LVS通過是保證芯片功能正確的關鍵。

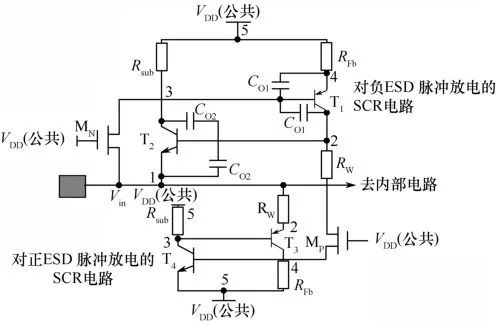

- 電氣規則檢查(ERC):ERC主要檢查版圖中潛在的電氣問題,這些問題可能不違反幾何設計規則,但會導致電路失效。例如,檢查是否存在浮空的柵極(Gate)、電源和地之間是否短路、襯底連接是否正確等。ERC規則通常也包含在LVS或獨立的規則文件中,是DRC和LVS的重要補充。

二、Calibre驗證文件的核心方法與編寫要點

- 規則文件結構:典型的Calibre規則文件采用層次化的語法結構。它通常包括頭文件聲明、層定義、規則主體等部分。層定義將版圖數據(GDS/OASIS文件中的層號)映射到Calibre內部用于運算的邏輯層。規則主體則使用豐富的命令和運算符(如AND、OR、NOT、SIZE、ENCLOSE等)來描述復雜的幾何與電氣約束。

- 層操作與衍生層:驗證的核心是對圖形層進行邏輯運算,生成“衍生層”。例如,要檢查金屬1(M1)與多晶硅(Poly)的最小間距,需要先定義M1層和Poly層,然后使用

SPACE命令對兩者進行間距檢查。通過組合不同的層操作,可以構建出非常復雜的檢查場景,如檢查天線效應(Antenna Rule)、阱間距(Well Proximity)等。

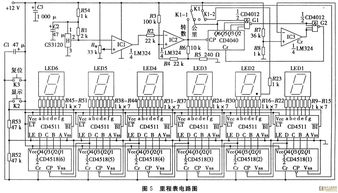

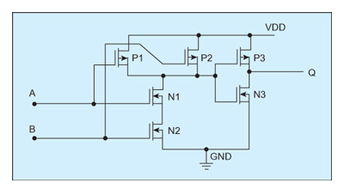

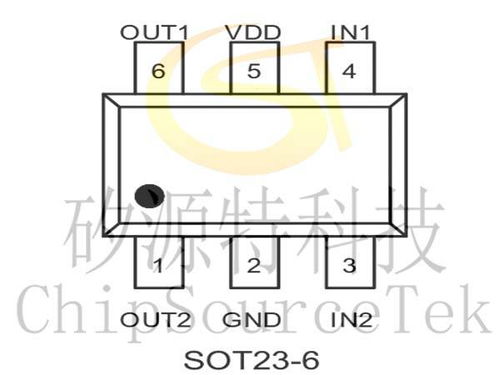

- 器件識別與屬性提取:在LVS文件中,最關鍵的部分是“器件識別”模塊。它通過一系列層操作,從版圖中“切割”并識別出一個個獨立的器件。例如,一個NMOS管可以通過有源區(Active)、多晶硅(Poly)以及N型注入層(N_imp)的交疊來定義。識別后,還需要提取器件的屬性,如MOS管的寬(W)和長(L)。這些信息將與原理圖網表中的器件參數進行比對。

- 連接關系提取:LVS的另一核心是提取連接關系。通過定義連接層(如金屬層、接觸孔/通孔層),Calibre可以自動生成版圖的電氣連接網表。驗證文件需要明確定義哪些層之間通過接觸孔相連,從而構建出完整的導電通路。

三、驗證流程與集成電路設計整合

在完整的集成電路設計流程中,Calibre驗證并非一次性工作,而是與版圖設計迭代并行的過程。

- 交互式驗證(Online Verification):現代版圖設計工具(如Cadence Virtuoso)通常與Calibre深度集成,支持在繪制版圖的同時實時或快速進行DRC和LVS檢查。這允許設計者及時發現并修正錯誤,極大提高了設計效率。

- 簽核驗證(Sign-off Verification):在版圖最終完成后,需要進行全面、嚴格的“簽核”驗證。這通常是離線的、批處理式的完整運行,確保在所有工藝角(Corner)下,DRC、LVS和ERC都完全通過。只有簽核驗證通過,版圖數據才能交付給代工廠進行掩模制作。

- 與寄生參數提取的協同:物理驗證通過后,通常還需要使用Calibre xRC等工具從驗證后的潔凈版圖中提取寄生電阻和電容(PEX),生成帶寄生參數的電路網表。將此網表反標(Back-annotate)到電路仿真器中,進行后仿真(Post-layout Simulation),以驗證版圖寄生效應是否影響電路性能(如速度、功耗、噪聲等)。這是確保設計成功的關鍵一步。

四、

Calibre驗證文件是連接CMOS模擬集成電路設計與制造的“法律文書”和“質量檢測標準”。掌握其基礎語法、理解DRC、LVS、ERC的核心原理與方法,并熟練將其融入迭代設計流程,是每一位模擬版圖工程師和芯片設計者的必備技能。一個潔凈、驗證通過的版圖,是芯片從設計藍圖變為物理實體的堅實保障。通過嚴謹的物理驗證,才能最大程度地降低流片風險,提高芯片的一次成功率。

如若轉載,請注明出處:http://www.aaaaadesign.cn/product/64.html

更新時間:2026-03-01 11:10:24