一文讀懂集成電路產(chǎn)業(yè)版圖設(shè)計過程 從電路到晶圓的精密藍(lán)圖

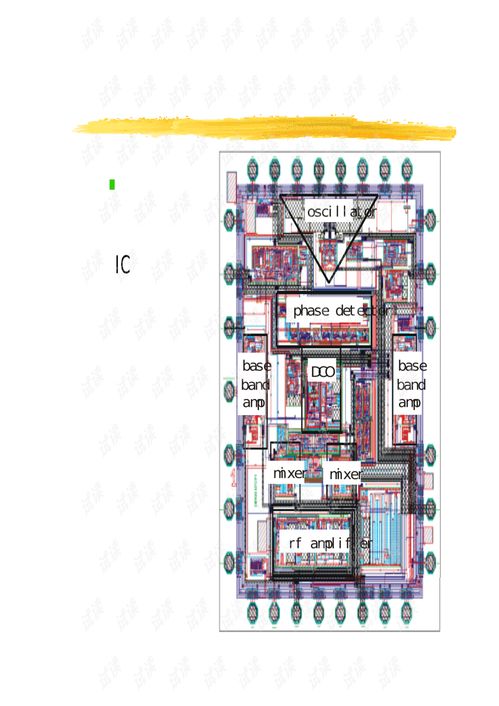

集成電路(IC)是現(xiàn)代電子產(chǎn)品的“大腦”和“心臟”,而其物理實現(xiàn)的核心環(huán)節(jié)便是版圖設(shè)計。它如同建筑工程的施工藍(lán)圖,將邏輯電路轉(zhuǎn)化為可在硅片上制造的幾何圖形。本文將系統(tǒng)解析集成電路版圖設(shè)計的全過程。

一、 版圖設(shè)計:連接設(shè)計與制造的橋梁

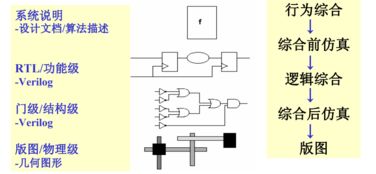

版圖設(shè)計處于集成電路設(shè)計流程的后端,是電路設(shè)計(前端)與芯片制造(后端)之間的關(guān)鍵紐帶。其核心任務(wù)是根據(jù)電路網(wǎng)表、工藝規(guī)則和性能要求,繪制出構(gòu)成芯片所有物理層的精確幾何圖形(如晶體管、互連線、接觸孔等)。這些圖形最終通過光刻等工藝轉(zhuǎn)移到硅片上,形成實際的電路結(jié)構(gòu)。

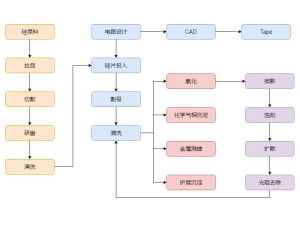

二、 版圖設(shè)計的核心流程

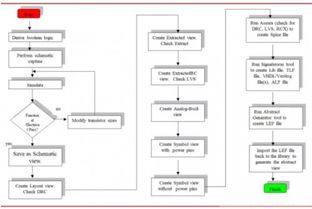

一個完整的版圖設(shè)計流程通常包含以下幾個關(guān)鍵步驟:

1. 規(guī)劃與布局

這是版圖設(shè)計的戰(zhàn)略階段。設(shè)計者需要根據(jù)芯片的功能、規(guī)模和性能指標(biāo)(如速度、功耗)進(jìn)行整體規(guī)劃,確定核心模塊(如CPU、存儲器、模擬模塊)的位置、形狀以及芯片的輸入/輸出(I/O)引腳排列。目標(biāo)是實現(xiàn)最優(yōu)的模塊間連線、最小的芯片面積和最佳的性能。

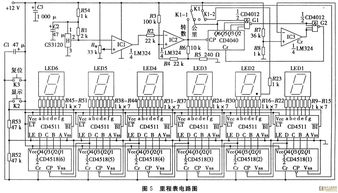

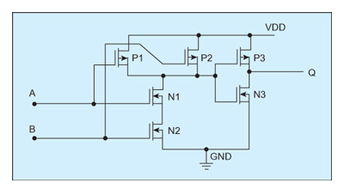

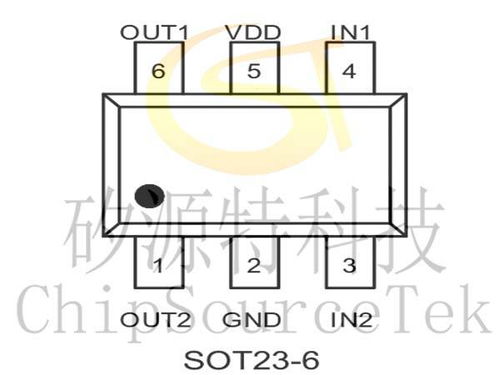

2. 電路單元設(shè)計

對于標(biāo)準(zhǔn)單元庫中的基本邏輯門(如與非門、觸發(fā)器)或定制化的模擬電路模塊,需要進(jìn)行晶體管級的版圖繪制。這一步驟需要嚴(yán)格遵守設(shè)計規(guī)則——由芯片制造廠提供的、確保芯片可制造性和良率的一系列幾何尺寸限制(如最小線寬、最小間距等)。

3. 布局

將數(shù)以億計的電路單元(從標(biāo)準(zhǔn)單元到宏模塊)按照規(guī)劃放置到芯片的版圖平面上。先進(jìn)的布局工具會自動化完成大部分工作,同時優(yōu)化單元位置以減少連線長度和信號延遲。

4. 布線

在單元之間根據(jù)電路連接關(guān)系(網(wǎng)表)繪制金屬互連線。這是一個極其復(fù)雜的步驟,通常分為全局布線(規(guī)劃連線的大致路徑通道)和詳細(xì)布線(在指定通道內(nèi)完成每一根線的精確繪制)。布線必須遵守多層金屬的布線規(guī)則,并避免串?dāng)_、電遷移等問題。

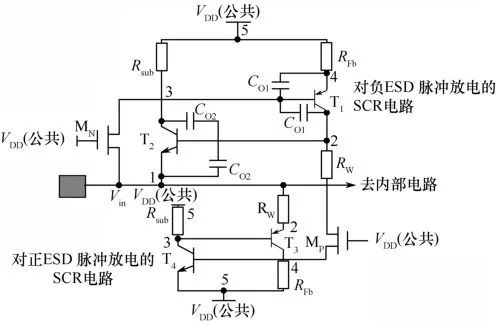

5. 物理驗證

版圖完成后,必須經(jīng)過嚴(yán)格驗證才能交付制造,主要包括:

- 設(shè)計規(guī)則檢查:檢查版圖是否完全符合制造工藝的設(shè)計規(guī)則。

- 電氣規(guī)則檢查:檢查是否存在短路、開路等電氣錯誤。

- 版圖與電路圖一致性檢查:確保繪制的物理版圖與原始的電路邏輯網(wǎng)表完全匹配。

- 寄生參數(shù)提取:從版圖中提取連線帶來的電阻、電容等寄生效應(yīng),并反標(biāo)回電路進(jìn)行仿真,以驗證性能是否達(dá)標(biāo)。

6. 數(shù)據(jù)交付

最終通過驗證的版圖,將轉(zhuǎn)換為一種標(biāo)準(zhǔn)的圖形數(shù)據(jù)格式(通常是GDSII或OASIS),連同相關(guān)的測試和封裝信息,一并交付給芯片制造廠(晶圓廠),用于制作光刻掩膜版。

三、 版圖設(shè)計的核心挑戰(zhàn)與趨勢

- 納米級挑戰(zhàn):隨著工藝進(jìn)入7納米、5納米甚至更小節(jié)點,物理效應(yīng)(如工藝波動、量子隧穿)愈發(fā)顯著,版圖設(shè)計必須與可制造性設(shè)計、可靠性設(shè)計深度融合。

- 設(shè)計復(fù)雜性:芯片集成度(晶體管數(shù)量)指數(shù)級增長,全手工設(shè)計已不現(xiàn)實,高度自動化的電子設(shè)計自動化工具鏈成為必備。

- 系統(tǒng)級協(xié)同:在先進(jìn)封裝(如2.5D/3D IC)中,版圖設(shè)計需跨芯片、跨中介層進(jìn)行協(xié)同規(guī)劃和優(yōu)化。

###

集成電路版圖設(shè)計是一門融合了電子工程、計算機科學(xué)和精密制造的藝術(shù)與科學(xué)。它要求設(shè)計者不僅精通電路原理,還需深刻理解制造工藝的物理限制。正是通過這一精密的“繪圖”過程,抽象的電路思想才得以轉(zhuǎn)變?yōu)閷崒嵲谠凇Ⅱ?qū)動萬物數(shù)字化的硅基芯片。隨著技術(shù)的演進(jìn),版圖設(shè)計將持續(xù)向著更高自動化、更智能化和更系統(tǒng)化的方向發(fā)展。

如若轉(zhuǎn)載,請注明出處:http://www.aaaaadesign.cn/product/60.html

更新時間:2026-03-01 20:28:22