集成電路設(shè)計 從原理到實踐的全方位指南

集成電路設(shè)計是現(xiàn)代電子技術(shù)的核心領(lǐng)域,涵蓋了從理論到實際應(yīng)用的全過程。本書旨在為初學(xué)者和專業(yè)人士提供系統(tǒng)性的知識框架,幫助讀者深入理解集成電路的設(shè)計原理、方法與工具。

一、集成電路設(shè)計概述

集成電路設(shè)計是指將數(shù)百萬甚至數(shù)十億個晶體管集成到單一芯片上的過程。它涉及電路設(shè)計、版圖設(shè)計、仿真驗證等多個環(huán)節(jié)。隨著工藝節(jié)點不斷縮小,設(shè)計復(fù)雜度日益增加,對設(shè)計人員的要求也越來越高。

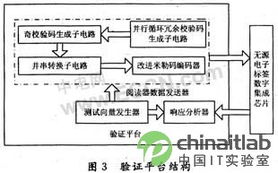

二、設(shè)計流程與方法

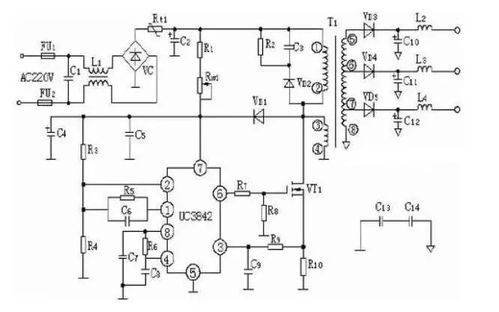

典型的集成電路設(shè)計流程包括:系統(tǒng)規(guī)劃、電路設(shè)計、物理設(shè)計、驗證測試等階段。現(xiàn)代設(shè)計方法主要分為全定制設(shè)計、半定制設(shè)計和可編程邏輯設(shè)計三大類,每種方法各有優(yōu)劣,適用于不同的應(yīng)用場景。

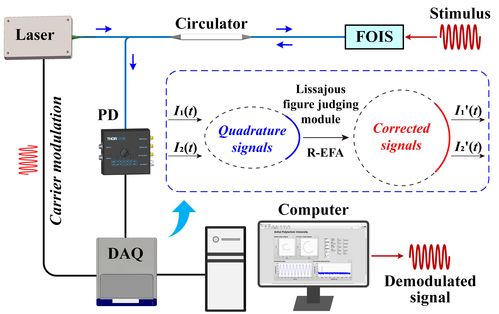

三、關(guān)鍵技術(shù)與工具

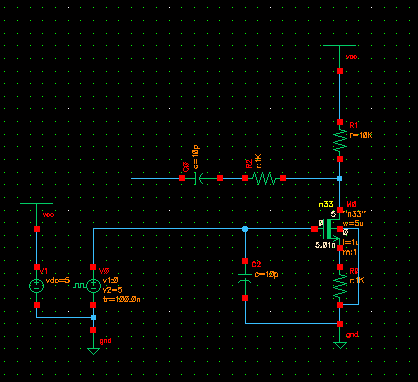

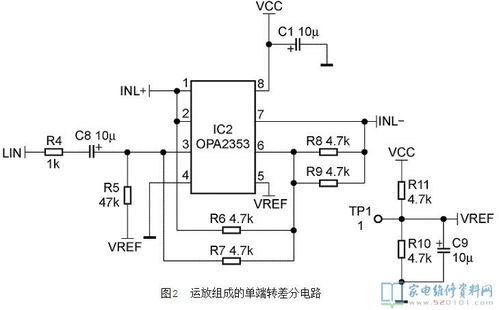

EDA(電子設(shè)計自動化)工具是集成電路設(shè)計的重要支撐。主流的EDA工具包括Cadence、Synopsys和Mentor Graphics等,它們提供了從電路仿真到版圖設(shè)計的完整解決方案。IP核復(fù)用、低功耗設(shè)計、信號完整性分析等關(guān)鍵技術(shù)也是現(xiàn)代集成電路設(shè)計的重點。

四、設(shè)計挑戰(zhàn)與發(fā)展趨勢

隨著工藝進入納米級別,集成電路設(shè)計面臨著功耗、散熱、時序收斂等嚴(yán)峻挑戰(zhàn)。未來,異構(gòu)集成、AI輔助設(shè)計、3D集成等新技術(shù)將為集成電路設(shè)計帶來新的發(fā)展機遇。

五、學(xué)習(xí)建議與實踐指導(dǎo)

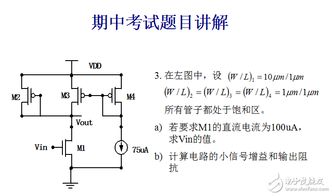

對于初學(xué)者,建議從基礎(chǔ)電路理論入手,逐步學(xué)習(xí)數(shù)字電路、模擬電路和半導(dǎo)體物理等知識。實際操作方面,可以從簡單的FPGA設(shè)計開始,逐步過渡到ASIC設(shè)計。同時,關(guān)注行業(yè)最新動態(tài)和技術(shù)發(fā)展趨勢也十分重要。

集成電路設(shè)計是一個需要持續(xù)學(xué)習(xí)和實踐的領(lǐng)域。通過系統(tǒng)學(xué)習(xí)理論知識和不斷積累實踐經(jīng)驗,設(shè)計人員能夠在這個快速發(fā)展的行業(yè)中保持競爭力,為電子產(chǎn)品的小型化、智能化和高效化做出貢獻。

如若轉(zhuǎn)載,請注明出處:http://www.aaaaadesign.cn/product/3.html

更新時間:2026-03-01 17:50:32